Kicking off with finite state machine in verilog, this technology has been widely used in digital design for decades due to its simplicity and effectiveness. Finite state machines are essentially a series of states that a system can be in, where each state is determined by an input and the system will transition to another state based on that input. This concept has been around since the late 19th century, but its applications have grown exponentially with the advent of technology. Today, finite state machines are used in a wide range of fields, from electronics and robotics to computer science and even medicine. They are used to implement complex behaviors in systems that need to respond to changing inputs, such as traffic lights, elevators, and even some types of artificial intelligence.

The purpose of using Verilog to design and implement finite state machines is to create a digital logic circuit that can implement the desired behavior using a hardware description language. Verilog is a popular language used in digital design and has been widely adopted by designers for its simplicity and effectiveness. In this Artikel, we will cover the different components of a finite state machine in Verilog, including registers, counters, and logic gates, and provide examples of Verilog code for implementing these components.

Finite State Machine Simulation and Verification

Finite State Machine (FSM) simulation and verification are crucial stages in the development and testing of digital circuits and systems. These processes ensure that the FSM behaves correctly, according to its design specifications, before it is implemented in hardware or software. This verification is essential because a small error in FSM design can lead to significant problems, affecting the system’s functionality and reliability.

Using Simulation Tools to Test a FSM’s Functionality

Simulation tools play a vital role in testing and verifying the behavior of a Finite State Machine in Verilog. These tools allow designers to model and simulate the FSM, applying various input scenarios to verify its correct operation. Commonly used tools include:

- ModelSim: A widely used simulator for digital circuits, which supports Verilog and VHDL languages.

- NGCsim: A Verilog simulator that provides simulation, debugging, and verification capabilities.

- Verilator: An open-source Verilog simulator that supports the simulation of digital circuits and systems.

Simulation tools enable designers to test the FSM under various conditions, such as different input sequences, clock frequencies, and power supply voltages. This helps identify potential issues and ensures the FSM operates correctly in various scenarios.

Verification Techniques for FSMs

Verification techniques for FSMs include property checking and assertion-based verification. These methods ensure that the FSM behaves correctly and meets the design specifications.

Property Checking

Property checking is a verification technique that ensures the FSM satisfies certain properties, such as:

- Transition properties: Verifying the FSM transitions between states correctly.

- Temporal properties: Ensuring the FSM satisfies temporal properties, such as always or never.

Assertion-Based Verification

Assertion-based verification involves inserting assertions into the FSM code to ensure it behaves correctly. Assertions can be used to:

- Check input/output relationships.

- Verify state transitions.

- Ensure correct behavior under various scenarios.

Assertions can be monitored during simulation, providing immediate feedback on any errors or unexpected behavior in the FSM.

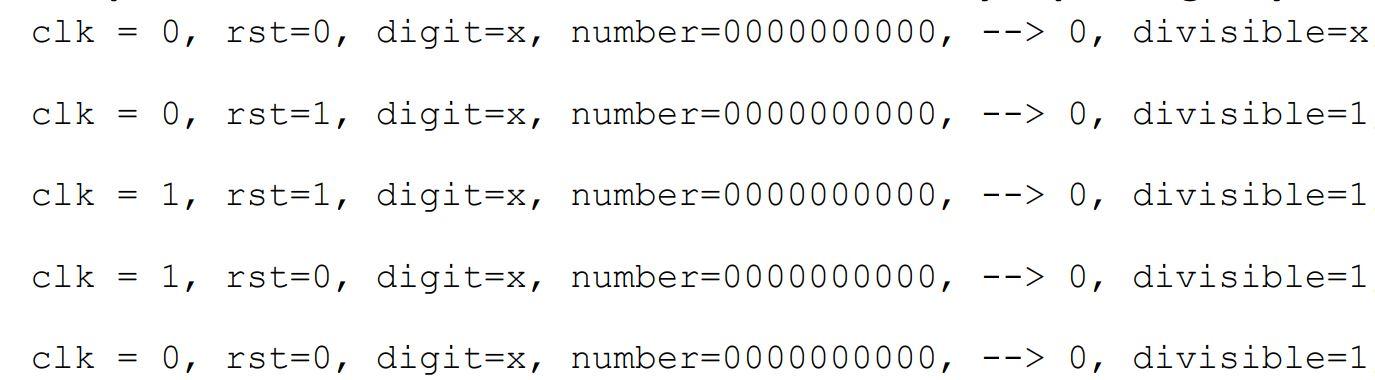

FSM Simulation Examples

To illustrate the importance of FSM simulation and verification, consider the following example:

A simple traffic light controller FSM in Verilog is designed to sequence through different states (red, yellow, and green) based on a clock signal. The FSM’s behavior is verified using simulation tools to ensure it operates correctly under various conditions, such as:

- Normal operation: Verifying the FSM transitions correctly through the states.

- Edge cases: Testing the FSM’s behavior when the clock signal is interrupted or the input is changed abruptly.

The simulation results can be analyzed to identify any potential issues and ensure the FSM meets the design specifications.

Finite State Machine Optimization Techniques in Verilog

Finite state machines (FSMs) are a fundamental component in digital design, and optimizing them for area and speed is crucial for achieving high-performance and low-power designs. In this section, we will explore various optimization techniques for FSMs in Verilog.

Method 1: Minimizing State Machines, Finite state machine in verilog

Minimizing the number of states in an FSM is an effective way to optimize its implementation. This can be achieved using algorithms like the minimization of the FSM’s transition table. The goal is to remove any redundant or equivalent states, which can reduce the number of states required for the same functionality.

FSMs can be minimized using algorithms like the Hopcroft algorithm.

A well-minimized FSM will have fewer states and thus a shorter transition table, resulting in a smaller area and faster execution speed.

Method 2: Using Lookup Tables (LUTs)

Lookup tables are a powerful technique for optimizing FSMs. LUTs are precomputed tables that store the next state of the FSM given a specific input combination. By using LUTs, the FSM can retrieve the next state directly from the table, rather than computing it through a complex set of logic gates.

This technique can be particularly effective when the FSM has a large number of states and inputs. LUTs can significantly reduce the area required for the FSM and improve its execution speed.

Method 3: Using Carry Chains

Carry chains are a technique used to optimize FSMs by reusing the carry signals from one state to the next. This can reduce the number of gates required for the FSM and improve its execution speed.

By using carry chains, the FSM can reduce the number of gates required for the same functionality, resulting in a smaller area and faster execution speed.

Method 4: Using Synthesis Tools

Modern synthesis tools, such as Synopsys Design Compiler and Cadence Genus, offer various optimization techniques for FSMs, including automatic state minimization, LUT utilization, and carry chain generation.

These tools can significantly reduce the area and improve the execution speed of the FSM, while also reducing the design time and effort required.

Method 5: Using Formal Verification

Formal verification tools, such as ModelSim and Cadence Conformal, offer various techniques for verifying the correctness of FSMs, including model checking and theorem proving.

By using formal verification, designers can ensure that their FSMs are correct and functional, while also identifying and fixing any errors or bugs.

Advanced Finite State Machine Topics in Verilog: Finite State Machine In Verilog

In the realm of digital design, finite state machines (FSMs) serve as the backbone of many control and data processing systems. Their ability to efficiently manage complex behaviors has led to their widespread adoption in numerous applications, including microprocessors, communication networks, and signal processing systems. As we delve into the advanced topics of FSM design in Verilog, we will explore the intricacies of pipelining, parallelism, and other high-performance techniques.

Pipelining in FSM Design

Pipelining is a fundamental concept in digital design, particularly in FSMs, where it enables the processing of multiple inputs in a single clock cycle. This technique involves breaking down the FSM into stages, each of which performs a specific task. By overlapping the execution of these stages, pipelining facilitates a significant increase in processing speed.

Pipelining = (Stage N + Stage (N-1) + … + Stage 0) * T

Where T represents the delay between stages. By minimizing T, the overall processing time can be substantially reduced.

Pipelining can be applied in various ways, such as:

- Input Pipelining: Breaking down the input processing into multiple stages, each handling a subset of the input bits.

- Combinatorial Pipelining: Using combinational logic to perform tasks that do not depend on the previous clock cycle.

- Sequential Pipelining: Using registers to store intermediate results and propagate them to subsequent stages.

By applying pipelining techniques, designers can create high-performance FSMs that efficiently manage complex behaviors.

Parallelism in FSM Design

Parallelism is another technique used to improve the processing speed of FSMs. By executing multiple tasks simultaneously, parallelism reduces the overall processing time and increases the throughput of the system. Verilog’s ability to create parallel threads using the ‘fork-join’ construct enables designers to harness the power of parallelism in FSM design.

Parallel Threads = T1 + T2 + … + T

Where T

Verilog’s ‘fork-join’ construct can be used to create parallel threads in FSM design as follows:

“`verilog

fork

// Thread 1: processing operation 1

begin

// operation 1 code

end

// Thread 2: processing operation 2

begin

// operation 2 code

end

join

“`

When executed in parallel, these threads can significantly improve the processing speed of the FSM.

High-Performance FSM Constructs in Verilog

Verilog provides two constructs, ‘always_latch’ and ‘always_comb’, which enable designers to create high-performance FSMs. The ‘always_latch’ construct is used to create combinational logic, while the ‘always_comb’ construct is used to create sequential logic.

‘always_latch’ = always_comb + no sequential dependencies

By using these constructs, designers can minimize sequential dependencies and create high-performance FSMs.

“`verilog

always_comb

begin

// combinational logic code

end

“`

The ‘always_comb’ construct is used to create combinational logic, while the ‘always_latch’ construct is used to create sequential logic. By using these constructs correctly, designers can create high-performance FSMs.

Complex FSMs with Multiple Clocks and Reset

In some cases, FSMs may require multiple clocks or reset signals to manage complex behaviors. Verilog provides the necessary constructs to handle these scenarios. By using the ‘always_comb’ and ‘always_latch’ constructs, designers can create FSMs with multiple clocks and reset signals.

“`verilog

always_comb

begin

// multiple clocks and reset logic code

end

“`

By using these constructs, designers can create complex FSMs that manage multiple clocks and reset signals.

Final Wrap-Up

In this discussion, we have covered the basics of finite state machines in Verilog, including their concept, components, design process, validation, optimization techniques and advanced topics. We have also discussed the importance of simulation and verification in FSM design, as well as methods for optimizing FSMs for area and speed. Finally, we have introduced some advanced topics in FSM, such as pipelining and parallelism, which are crucial for high-performance FSMs.

General Inquiries

What is a finite state machine?

A finite state machine is a mathematical model used to describe the behavior of a system that can be in one of a finite number of states. It is a simple, yet powerful tool for modeling and analyzing complex systems.

Why use Verilog to design and implement finite state machines?

Verilog is a widely used hardware description language that is well-suited for designing and implementing digital logic circuits, including finite state machines. It is widely adopted by designers due to its simplicity and effectiveness.

What are the different components of a finite state machine in Verilog?

The different components of a finite state machine in Verilog include registers, counters, and logic gates. These components are used to implement the state register and control logic of the FSM.